# Registered multilayer gravure printing of electronic thin film devices

Jürg Schleuniger, Nenad Marjanović, Christian Zschokke, Frédéric Zanella, and Rolando Ferrini

CSEM Muttenz, CSEM Centre Suisse d'Electronique et de Microtechnique SA, Tramstrasse 99, CH-4132 Muttenz, Switzerland

High quality printing equipment is a key enabler for printed electronics produced at low cost on large area, flexible substrates. In the framework of the CTI project SWiss Precision Electronic GRAvure PrintEr (SWIPEGRAPE), Centre Suisse d'Électronique et de Microtechnique (CSEM) supported the company Norbert Schläfli Maschinen Zofingen (NSMZ) to develop and validate a high precision laboratory gravure printing machine (Labratester II) for the fabrication of printed thin film devices e.g. single thin film transistors and inverters. Due to the high precision of the alignment system, Labratester II enables layer-bylayer printing with registration in the range of a few micrometres across 7 inch flexible or rigid substrates.

The results shows that the Labratester II is a versatile tool to close the gap between lab and production. In particular it demonstrates the capabilities for prototyping demonstrators, screening materials and refining processes before scale-up production of printed electronics. In addition the outcome shows that gravure printing is a suitable technology for printed electronics.

### Labratester II

The Labratester II is a lab-scale, high resolution gravure printing system based on a Granite stone plate. This stone plate (face grinded in a precision of 300 nm) is directly used for the air-lubricated bearing carriage (vacuum chuck). This carriage is driven by a linear motor. The fully Chromium cylinders are direct laser engraved and driven by a torque motor.

- Printing area 7x7" (200 x 200mm)

- Registration in the range of a few micrometer

- Able to print on flexible and rigid (glass) substrate

Labratester II

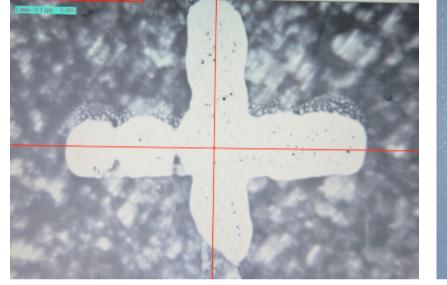

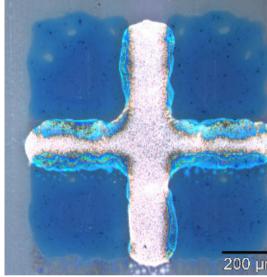

Alignment marks (screen view) and microscope image of over printed alignments mark (silver ink and UVcross-linkable blue ink).

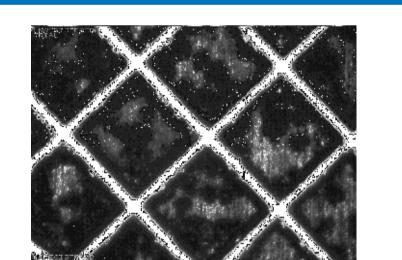

## Cylinder engraving and prints

Microscope Image: **Engraved cavities incl.** patterning

## Design

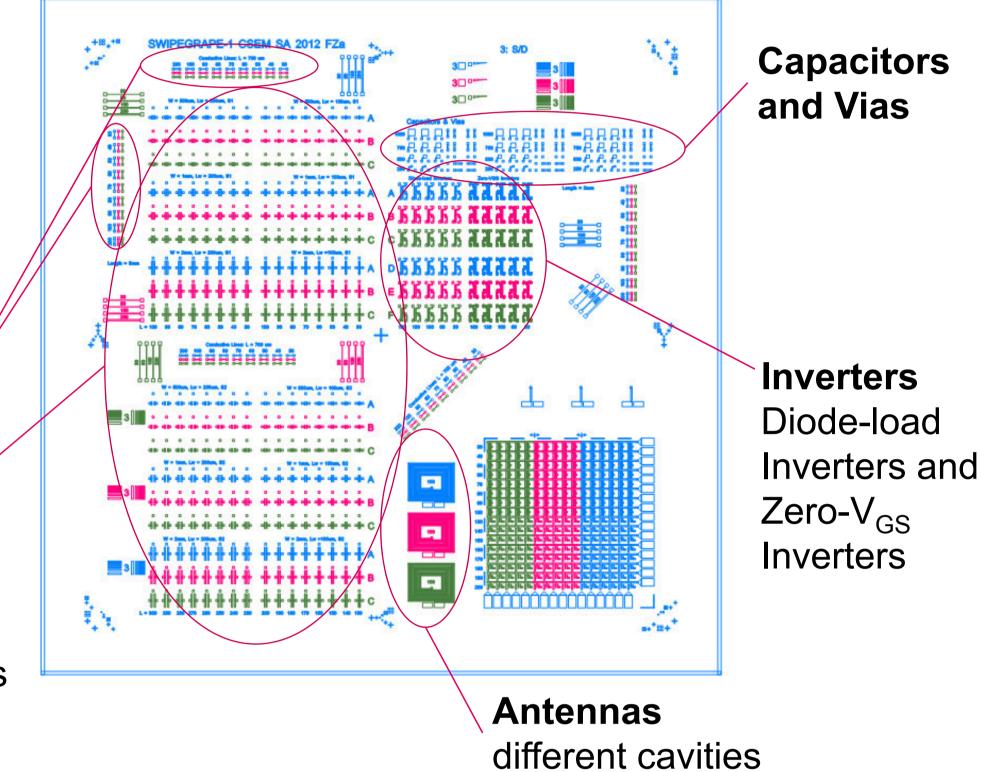

The cylinder design includes variation of different devices in different dimensions and engraving cavities:

- Single Transistors

- Inverters

- Antennas

- Vias

- Capacitors

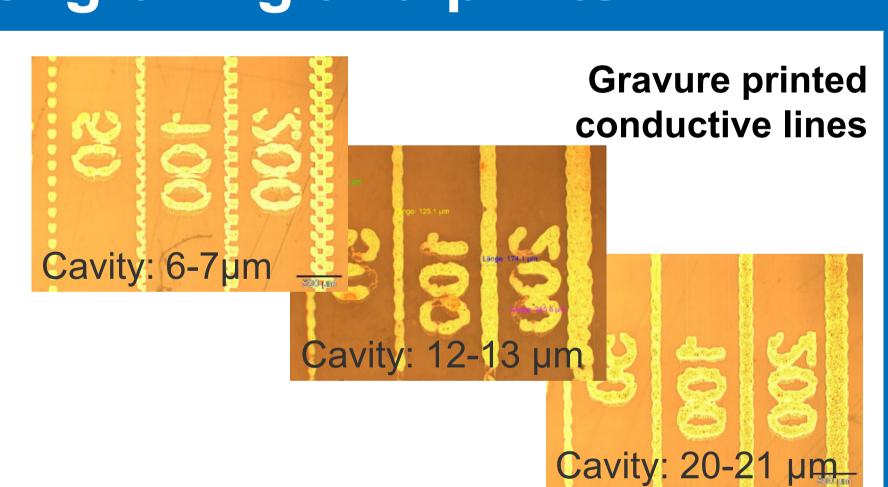

Conductive lines

#### **Conductive lines**

#### Single Transistors Variations in

- Channel length (L)

- Channel Width (W)

- **Engravings Cavities**

## Printed layer and device

printed

channel source/drain

gravure printed transistor

#### **Commercially available Materials:**

Silver ink: InkTec PR-020

Printed device

Semiconductor, Dielectric, Contact modification: Merck Lisicon

Substrate: Melinex ST506

#### Results Single Transistor and Inverters Transfer Forward Transfer and Output Transfer curves of an Reverse - r Id(Vd=0.0) curves of single OTFT inverter with $V_{DD} = 20V$ - Id(Vd=-5.0)Current Id (A) -Id(Vd=-10.0)- r Id(Vd=-10.0) —— Id(Vd=-15.0) r Id(Vd=-15.0)- Id(Vd=-20.0)- r ld(Vd=-20.0) Drain <del>-</del> ld(Vd=-25.0) Ig(Vd=-5.0)lg(Vd=-10.0)Ig(Vd=-15.0)-10 -15 -20 -25 -30 -15 Ig(Vd=-20.0) **V**<sub>IN</sub> [V] - lg(Vd=-25.0) Gate Voltage Vg (V) - lg(Vd=-30.0) 10.5V 1.107 10<sup>-2</sup> cm<sup>2</sup>/Vs Mobility: --- Sqrt[Id(Vd=-30.0)] Output Gain: 2.26 Threshold: -4.035 V -2.0x10<sup>-1</sup> NM<sub>MEC</sub>: 2.09V Current Id (A) On/Off: 1.924 10<sup>8</sup> ---- Id(Vg=0.0) - r Id(Vg=0.0) -1.5x10 ---- Id(Vg=-5.0) 0.6 V/dec - r Id(Vg=-5.0) Id(Vg=-10.0) $3.645\ 10^{-3}$ Ig/Id |<sub>Vgmax</sub>: -1.0x10 - - r Id(Vg=-10.0)— Id(Vg=-15.0) $Id_{max}L/W$ : 9.252 10<sup>-9</sup> - r Id(Vg=-15.0) ---Id(Vg=-20.0) -5.0x10 - - r ld(Vg=-20.0) —— Id(Vg=-25.0) - - r ld(Vg=-25.0) The presented transistors and inverters are based on Gold source/drain electrodes (patterned by gravure-printed —— Id(Vg=-30.0) photoresist), gravure printed semiconductor and dielectric. Gate electrode was evaporated due to the mismatch - - r Id(Vg=-30.0)of solvent of the printed conductors and dielectric layers. The used materials are commercially available. -15 -20 -10 Nevertheless entire printed transistors was demonstrated with proprietary materials. 10 V<sub>IN</sub> [V] Drain Voltage Vd (V)

acknowledgements

We gratefully acknowledge the financial support from the Commission for Technology and Innovation CTI; Project 13596.1 PFFLI-NM

**CSEM Muttenz** F +41 61 690 6000 CH-4132 Muttenz T +41 61 690 6011 Tramstrasse 99